员工姓名:张海洋

班 级:测控2018-02班

指导教师:王雪梅

毕设题目:嵌入式多通道法兰连接螺栓应力在线监测系统设计

一、概况

1.选题意义

法兰(Flange)又称为法兰盘或凸缘盘,是筒式结构、轴式结构与管道结构之间相互对接、传递力与变形的主要机械形式,通常出现于待连接结构的端面;法兰盘分为螺栓连接法兰和焊接法兰。

法兰连接具有构造结构简单、可操作性好等特点,因此在工业结构中应用广泛。螺栓法兰通过螺栓实现构件之间的连接,起着承载、密封或传递载荷等作用,如果连接螺栓失效或发生松动,将严重影响设备的正常工作,产生安全隐患,甚至导致严重的后果。因此对法兰连接螺栓的检测检修十分重要。

综合法兰连接螺栓应力监测的重要意义,本次毕业设计计划研制一种基于超声波应力检测法的嵌入式多通道法兰连接螺栓应力在线监测系统。本系统研究的特点为:(1)精度高:利用超声波应力监测法,基于声弹性效应,测量精度比传统方法高。(2)具有自动在线监测能力:用远程自动监测系统代替传统的人工现场检测、用实时监测设备在运行中螺栓的状态代替传统的定期停机检测。(3)具有远程监测能力:位于生产现场的下位机可将监测数据通过以太网传输至上位机,上位机中的程序一旦发现故障立即报警。因此生产人员不用在现场就可以实时观察设备运行情况。(4)具有多通道监测能力:整套系统可对多台机械设备上的多个法兰盘上的多个螺栓进行监测,一旦发现其中某一个发生故障,可以立即定位、报警。

2.任务分解

硬件部分任务分解:

(1)超声波探头的选型。(2)设计、调试超声波采集调理电路,具体包含:滤波放大电路、A/D转换电路、多路模拟通道等。(3)嵌入式系统核心控制器的选型:本次毕业设计选择ZYNQ作为嵌入式系统的核心控制器。

程序部分任务分解:

(1)开发PL(FPGA)端的程序。(2)开发PS(ARM)端的程序。(3)开发远程监控计算机中的程序。

系统试验任务分解:

(1)连接超声波换能器、多路超声波激励与采集电路、ZYNQ核心板、远程监控计算机这四个部分组成完整的系统。(2)进行电路、下位机、上位机联合调试,协调各个模块间的信号传递与通信。观察系统能否正常反应出螺栓应力变化。

二、已完成工作

(一)方案设计

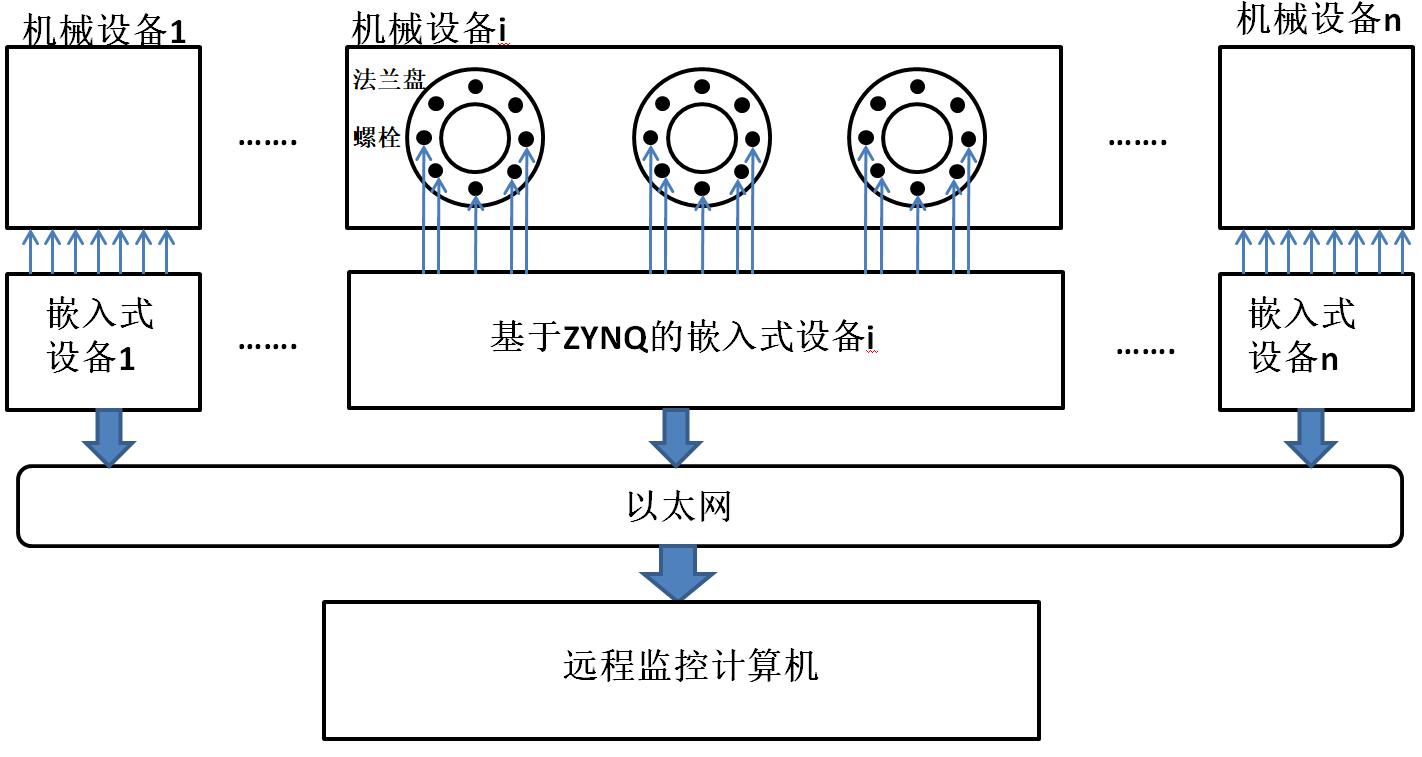

1.监测系统整体结构

图1 监测系统整体结构

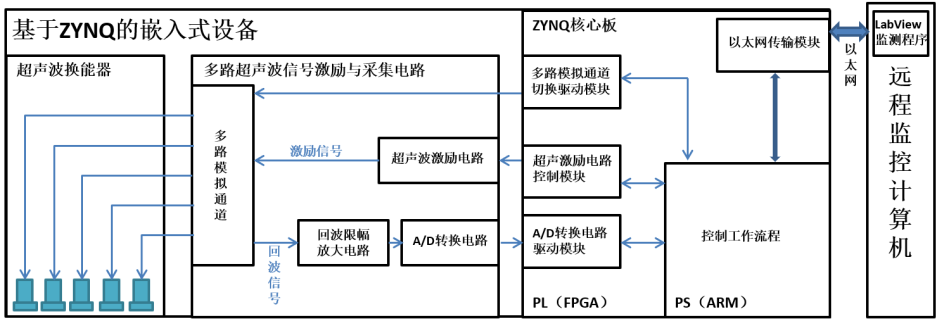

2.单套基于ZYNQ的嵌入式设备的硬件方案设计

图2 单套基于ZYNQ的嵌入式设备的硬件设计方案

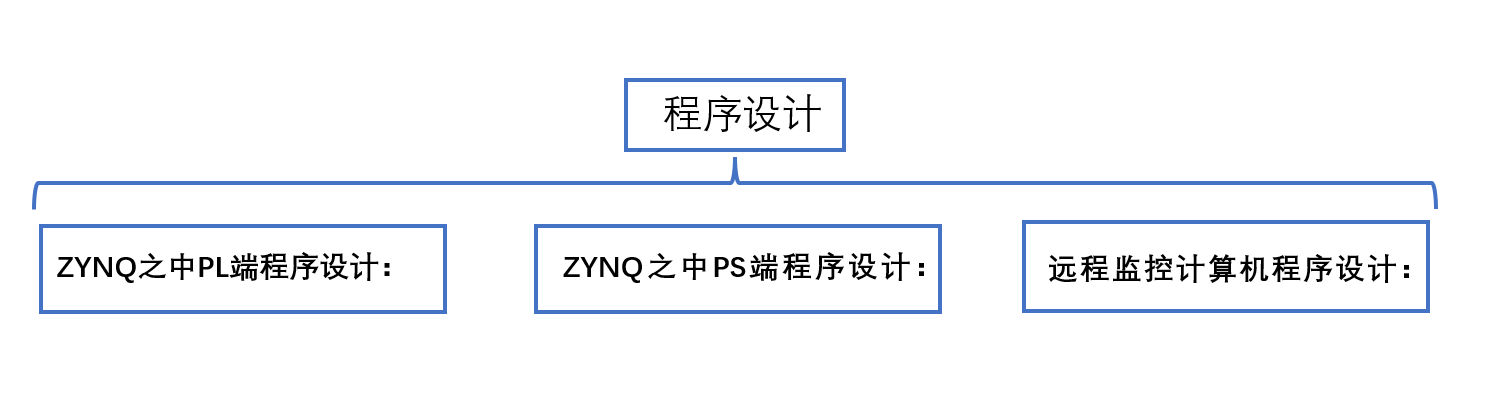

3.单套基于ZYNQ的嵌入式设备的程序方案设计

图3 单套基于ZYNQ的嵌入式设备的程序设计

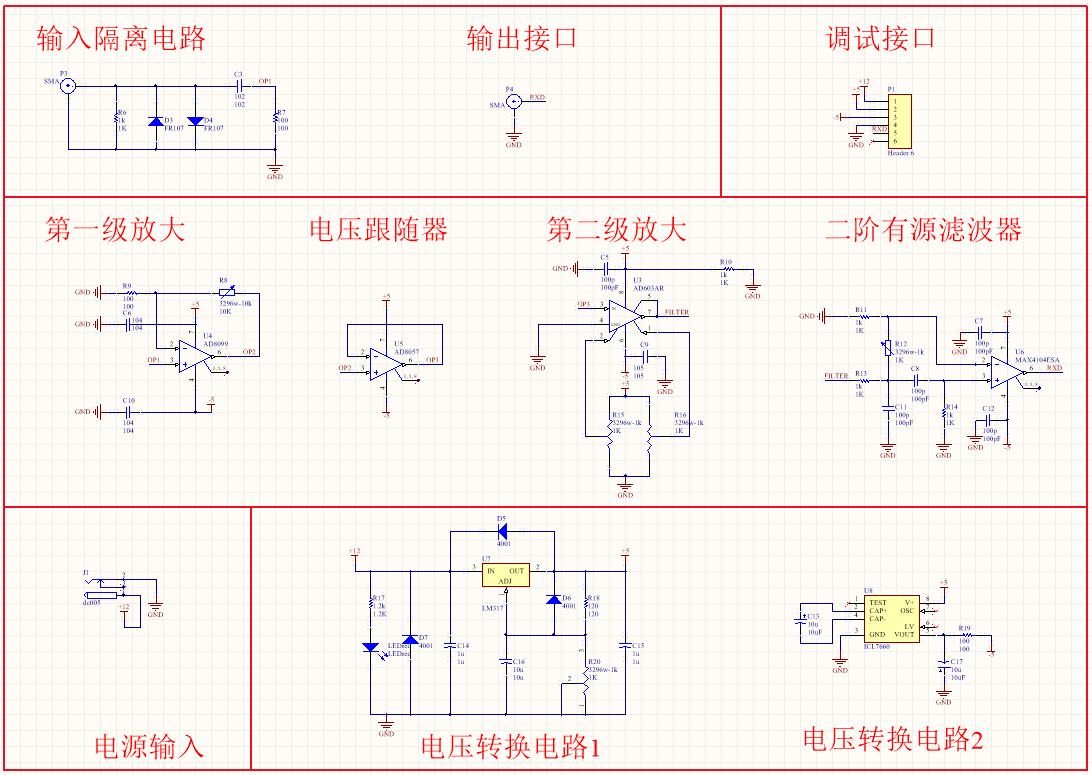

(二)放大滤波硬件电路设计

放大滤波电路由两级同相比例放大电路、一级电压跟随器、一级滤波放大电路构成,可以将频率为5MHz、峰峰值为几十mV左右的超声回波信号放大至+-5V。

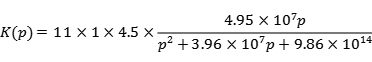

经过计算,可以得到放大滤波电路的传递函数为:

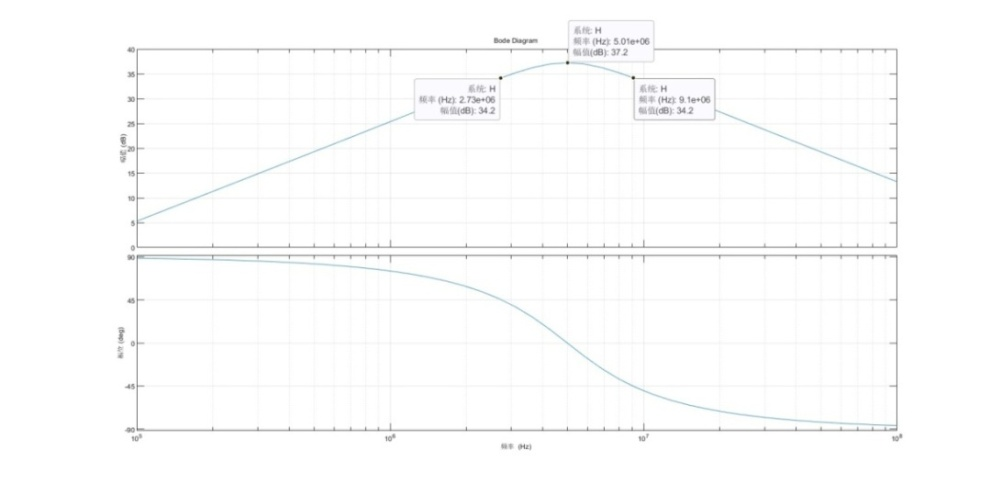

在Matlab中绘制该传递函数的幅频特性和相频特性如下图所示:

图4 幅频特性与相频特性理论计算结果

使用multisim进行仿真,仿真结果如图5所示:

图5 放大滤波电路仿真分析结果

绘制电路原理图如图6所示:

图6 电路原理图

(三)ZYNQ程序设计

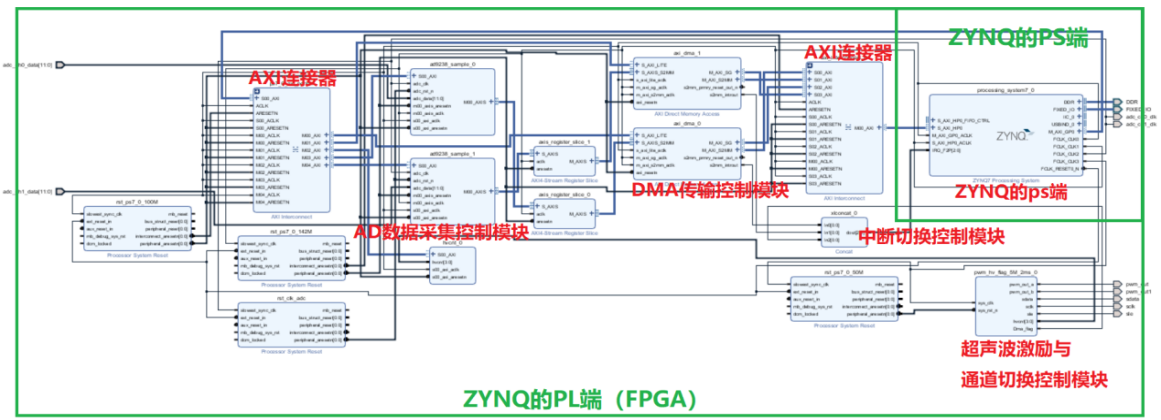

1.基于ZYNQ的嵌入式硬件系统搭建及FPGA程序设计:

图7 FPGA模块RTL原理图

如图7 FPGA模块RTL原理图,其工作流程大概为:激励信号与采样通道控制模块负责输出激励信号以及通道的切换,AD9238采样模块负责控制外部AD采集模块采集数据,采集到的数据经过DMA控制模块以DMA数据传输方式把数据传输到PS的内存DDR之中去。在PS之中,ARM把数据从内存DDR中读出,计算渡越时间,把计算结果通过以太网控制器Ethernet0发送给上位机。下面对各个模块进行简单介绍:

1.1 AD采集控制模块

AD采集控制模块采用状态机的方式进行编写,如下图所示:

图8 采集控制模块程序状态机

1.2超声波激励与通道控制模块

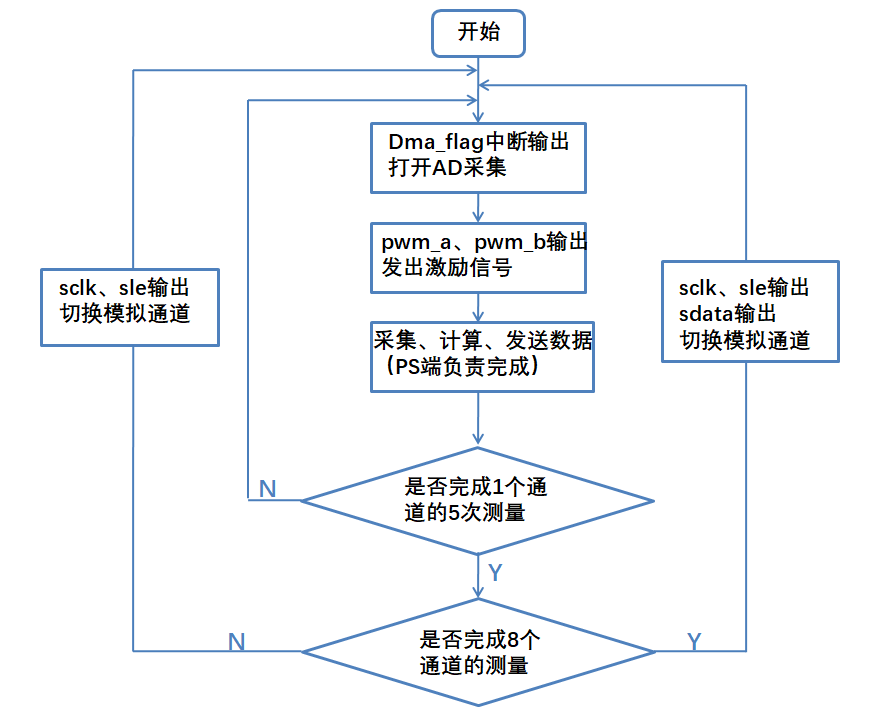

超声波激励与通道控制模块的工作流程图如下图所示:

图9 PL端程序工作流程

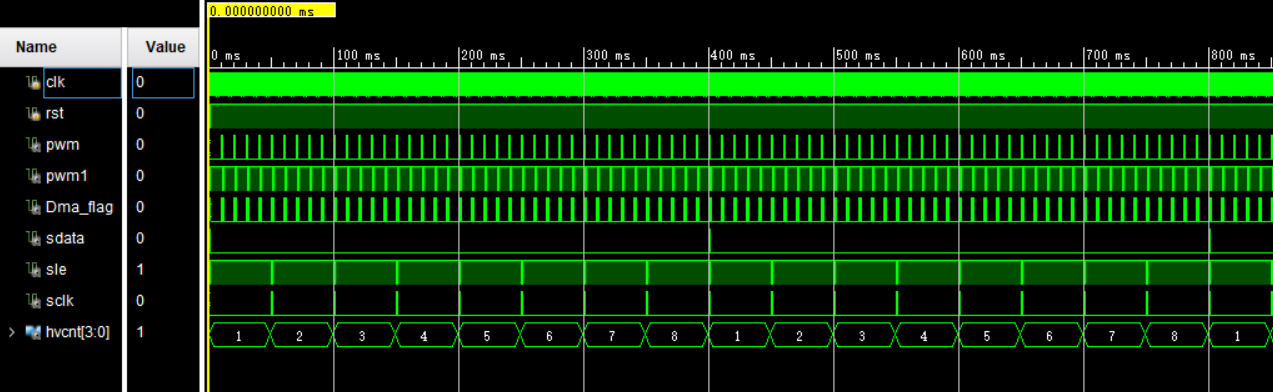

时序仿真结果如下图所示:

图10 仿真时序图

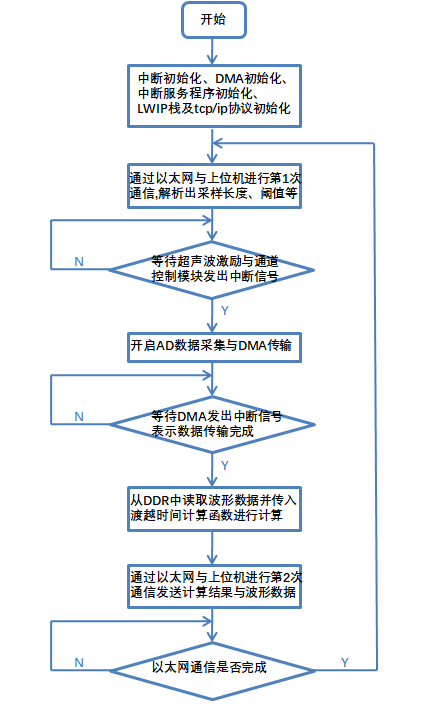

2.ARM程序设计

程序使用C语言进行编写,主要负责接收AD传来的数据,计算渡越时间,并将计算结果与其对应的波形数据发送至上位机。其中,接收AD传来的数据使用DMA的方式实现,将数据直接存入内存,不需要CPU一直控制。计算渡越时间使用电平比较法和最大峰值过零点法实现,编写了相应的程序。对于以太网数据传输,本系统采用TCP/IP协议作为网络通信协议,使用LWIP协议栈来实现。

图11 PS端程序流程图

下面对程序中计算渡越时间的部分和以太网传输的部分做详细的介绍:

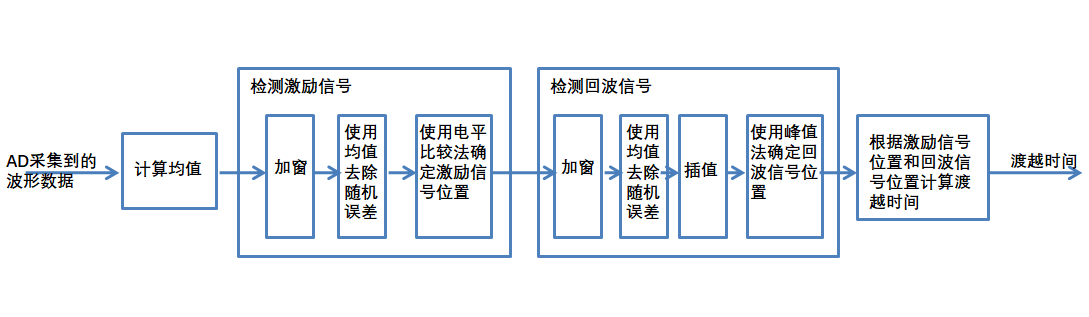

2.1渡越时间计算程序设计

时间的计算过程如下图所示:

图12 渡越时间计算流程图

2.2以太网传输程序

制定传输层数据段(用户数据)的数据格式如下表所示:

获取板卡信息:

(1)询问命令(上位机发送至开发板)

表1询问命令协议格式

(2)应答命令(开发板发送至上位机)

表2 应答命令协议格式

字节数 |

命令信息 |

1 |

0x00:表示查询 |

6 |

下位机MAC地址 |

4 |

下位机IP地址 |

4 |

采样频率 |

获取数据:

(3)控制命令(由上位机发送数据请求)

表3 控制命令协议格式

字节数 |

命令信息 |

1 |

0x01:表示控制 |

4 |

采样长度 |

2 |

阈值 |

2 |

加窗位置 |

(4)应答数据(开发板向上位机发送数据)

表4 应答数据协议格式

字节数 |

命令信息 |

5 |

TargetHeader |

1 |

通道号 |

8 |

渡越时间 |

4096 |

波形数据 |

三、下一步工作计划

4.13日至4.18日:完成基于LabVIEW的上位机程序设计,其中3天时间用于程序编写,2天时间用于程序调试。

4.19日至4.30日:开始进行系统试验,先用3天时间完成下位机、上位机联合程序调试,再用3天时间完成试验方案设计,最后用5天时间完成试验。

5.1日之后:分析实验数据,开始撰写毕业论文。

问题一:设计过程中使用了几块开发板?

回答:设计过程中使用了1块ZYNQ开发板,1块AD9238采样模块。其中ZYNQ开发板上使用的是ZYNQ-7000系列的芯片,它是一块SOC,上面集成了ARM与FPGA。

问题二:AD9238采集到的数据是如何传入ARM之中的?

回答:AD9238传来的数据,首先经过由FPGA引脚引出的排针进入到FPGA之中 。进入到FPGA之中的数据,通过PS与PL之间的HP接口,以DMA的方式存入到PS部分的内存DDR之中。ARM再从内存之中读取数据。

问题二:AD9238模块与 ZYNQ开发板通过排针连接的方式,是否能够支持DMA传输的速率?

回答:从理论上来讲是可行的,但是真实的效果需要在做实际的系统试验时进行测试。

首先感谢王雪梅老师在进行毕业设计过程中给予我的指导,感谢答辩组老师对我目前阶段所做工作的认可。

在进行毕业设计的过程中,我有许多收获。首先,为了完成此次设计,我复习了许多专业课知识,并且在实际设计中又对它们产生了新的理解。比如为了完成放大滤波电路的设计,我用到了《模拟电子技术》、《控制工程》等课程的基础知识,这让我更加深刻地认识到了专业基础知识的重要性。其次,为了完成此次设计,我还学习了许多新的知识,比如ZYNQ开发等。这让我深感自己知识储备的不足,还需要不断继续努力学习。

目前毕业设计的时间已经过半,我需要更加努力完成后面的工作,争取取得更加优异的成绩。